### Week 13 An Introduction to PIC microcontrollers

# Advantages of PIC

- It is a RISC (Reduced Instruction Set Computer) design

- Only thirty seven instructions to remember

- Its code is extremely efficient, allowing the PIC to run with typically less program memory than its larger competitors.

- It is low cost, high clock speed

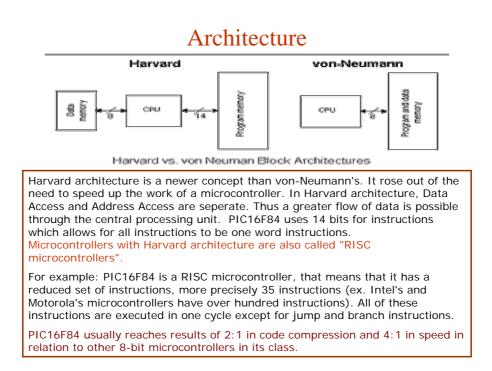

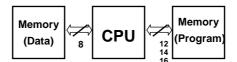

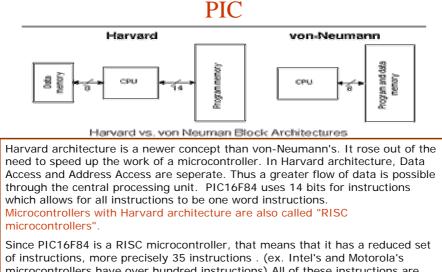

# Harvard Architecture

- Used mostly in RISC CPUs

- Separate program bus and data bus: can be different widths!

- For example, PICs use:

- Data memory (RAM): a small number of <u>8bit</u> registers

- Program memory (ROM): 12bit, 14bit or 16bit wide (in EPROM, FLASH, or ROM)

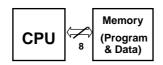

# Von-Neumann Architecture

- Used in: 80X86 (PCs), 8051, 68HC11, etc.)

- Only one bus between CPU and memory

- RAM and program memory share the same bus and the same memory, and so must have the same bit width

- Bottleneck: Getting instructions interferes with accessing RAM

### Complex Instruction Set Computer (CISC)

Traditionally, CPUs are "CISC"

- Used in: 80X86, 8051, 68HC11, etc.

- Many instructions (usually > 100)

- Several addressing modes

- Usually takes more than 1 internal clock cycle (Tcyc) to execute

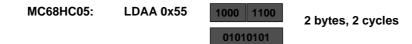

- Example:

# PICs and most Harvard chips are "RISC"

Reduced Instruction Set Computer (RISC)

- Used in: SPARC, ALPHA, Atmel AVR, etc.

- Few instructions (usually < 50)

- Only a few addressing modes

- Executes 1 instruction in 1 internal clock cycle (Tcyc)

- Example:

PIC16CXXX: MOVLW 0x55

1100XX 01010101 1 word, 1 cycle

# The PIC Family: Cores

PICs come with 1 of 4 CPU 'cores':

- 12bit cores with 33 instructions: 12C50x, 16C5x

- 14bit cores with 35 instructions: 12C67x,16Cxxx

- <u>16bit</u> cores with 58 instructions: 17C4x,17C7xx

- 'Enhanced' 16bit cores with 77 instructions: 18Cxxx

PICs require a clock to work.

- Can use crystals, clock oscillators, or even an RC circuit.

- Some PICs have a built in 4MHz RC clock

- Not very accurate, but requires no external components!

- Instruction speed = 1/4 clock speed (Tcyc = 4 \* Tclk)

- All PICs can be run from DC to their maximum spec'd speed:

| 12C50x          | 4MHz  |

|-----------------|-------|

| 12C67x          | 10MHz |

| 16Cxxx          | 20MHz |

| 17C4x / 17C7xxx | 33MHz |

| 18Cxxx          | 40MHz |

# The PIC Family: Program Memory

PIC program space is different for each chip.

Some examples are:

12C508 512 12bit instructions 16C711 1024 (1k) 14bit instructions 16F877 8192 (8k) 14bit instructions 17C766 16384 (16k) 16bit instructions

# The PIC Family: Program Memory

PICs have two different types of program storage:

<u>1- EPROM (Erasable Programmable Read Only Memory)</u>

- Needs high voltage from a programmer to program (~13V)

- · Needs windowed chips and UV light to erase

- Note: One Time Programmable (OTP) chips are EPROM chips, but with no window!

- PIC Examples: Any 'C' part: 12C50x, 17C7xx, etc.

- 2- FLASH

- Re-writable

- Much faster to develop on!

- Finite number of writes (~100k Writes)

- PIC Examples: Any 'F' part: 16F84, 16F87x, 18Fxxx (future)

# The PIC Family: Data Memory

PICs use general purpose "file registers" for RAM (each register is <u>8bits</u> for all PICs)

Some examples are:

| 12C508 | 25 Bytes RAM                                     |

|--------|--------------------------------------------------|

| 16C71C | 36 Bytes RAM                                     |

| 16F877 | 368 Bytes (plus 256 Bytes of nonvolatile EEPROM) |

| 17C766 | 902 Bytes RAM                                    |

# The PIC Family: Control Registers

### PICs use a series of "special function registers" for controlling peripherals and PIC behaviors.

Some examples are:

STATUS Bank select bits, ALU bits (zero, borrow, carry)

INTCON Interrupt control: interrupt enables, flags, etc.

TRIS Tristate control for digital I/O: which pins are 'floating'

TXREG UART transmit register: the next byte to transmit

# The PIC Family: Peripherals

# Different PICs have different on-board peripherals

#### Some common peripherals are:

- Tri-state ("floatable") digital I/O pins

- Analog to Digital Converters (ADC) (8, 10 and 12bit, 50ksps)

- Serial communications: UART (RS-232C), SPI, I<sup>2</sup>C, CAN

- Pulse Width Modulation (PWM) (10bit)

- Timers and counters (8 and 16bit)

- Watchdog timers, Brown out detect, LCD drivers

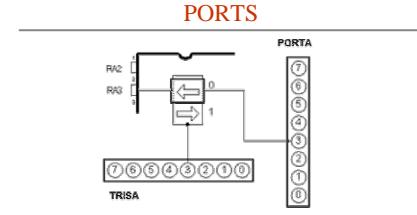

# PIC Peripherals: Ports (Digital I/O)

- All PICs have digital I/O pins, called 'Ports'

- the 8pin 12C508 has 1 Port with 4 digital I/O pins

- the 68pin 17C766 has 9 Ports with 66 digital I/O pins

- Ports have 2 control registers

- TRISx sets whether each pin is an input or output

- PORTx sets their output bit levels

- Most pins have 25mA source/sink (directly drives LEDs

# Microcontrollers in General

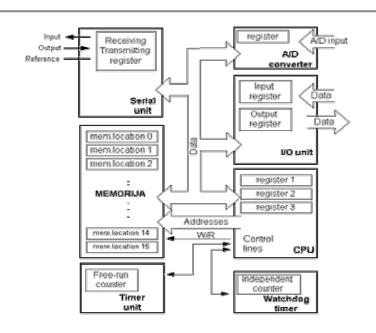

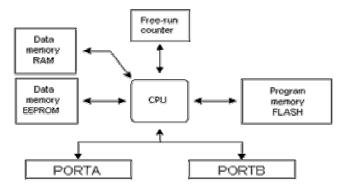

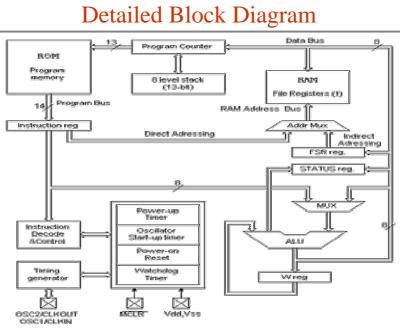

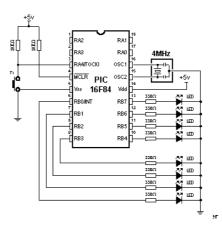

**PIC16F84** belongs to a class of 8-bit microcontrollers of RISC architecture. •**Program memory** (FLASH)- for storing a written program. Since memory made in FLASH technology can be programmed and cleared more than once, it makes this microcontroller suitable for device development.

•EEPROM - data memory that needs to be saved when there is no supply. It is usually used for storing important data that must not be lost if power supply suddenly stops. For instance, one such data is an assigned temperature in temperature regulators. If during a loss of power supply this data was lost, we would have to make the adjustment once again upon return of supply. Thus our device looses on self-reliance.

•RAM - data memory used by a program during its execution.

In RAM are stored all inter-results or temporary data during run-time.

•PORTA and PORTB are physical connections between the microcontroller and the outside world. Port A has five, and port B eight pins.

•CENTRAL PROCESSING UNIT has a role of connective element between other blocks in the microcontroller. It coordinates the work of other blocks and executes the user program.

### PIC

•FREE-RUN TIMER is an 8-bit register inside a microcontroller that works independently of the program. On every fourth clock of the oscillator it increments its value until it reaches the maximum (255), and then it starts counting over again from zero. As we know the exact timing between each two increments of the timer contents, timer can be used for measuring time which is very useful with some devices.

PIC16F84 microcontroller outline

microcontrollers have over hundred instructions) All of these instructions are executed in one cycle except for jump and branch instructions.

PIC16F84 usually reaches results of 2:1 in code compression and 4:1 in speed in relation to other 8-bit microcontrollers in its class.

# Procedure

The PIC16f84 is an 18-pin 14-bit embedded micro featuring electronically erasable programmable read-only memory (EEPROM). The essential steps are:

Step 1: On a PC, type the program, successfully compile it and then generate the HEX file.

Step 2: Using a PIC16F84 device programmer, upload the HEX file into the PIC16F84. This step is often called "burning".

Step 3: Insert your PIC16F84 into your circuit, power up and verify the program works as expected. This step is often called "dropping" the chip. If it isn't, you must go to Step 1 and debug your program and repeat burning and dropping.

Embedded micros having EPROM versus those with EEPROM require a fourth step - the program must be erased using ultraviolet light before starting again at Step 1. However the PIC16F84 uses EEPROM and is what makes it popular the device programmer erases the program without ultraviolet light.

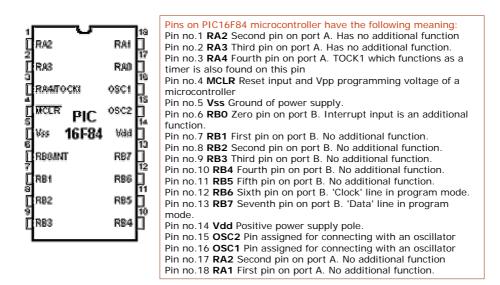

**PIN Description**

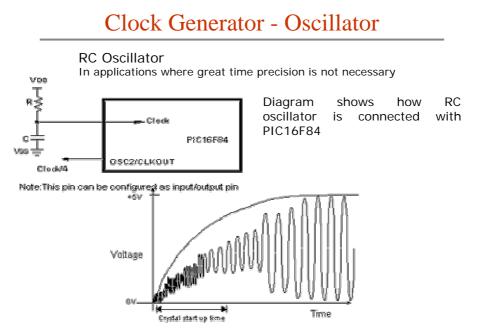

# Clock Generator - Oscillator

#### Types of oscillators

Crystal oscillator and resistor-capacitor (RC) are the ones that are used most frequently, these are the only ones we will mention here. Microcontroller type with a crystal oscillator has in its designation XT, and a microcontroller with resistor-capacitor pair has a designation RC.

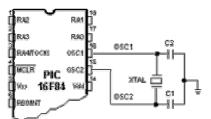

Connecting the quartz oscillator to give clock to a microcontroller

Signal of an oscillator clock after receiving the supply of a microcontroller

# Clock/Instruction Cycle

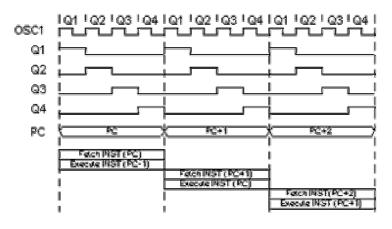

Clock from the oscillator enters a microcontroller via OSC1 pin where internal circuit of a microcontroller divides the clock into four even clocks Q1, Q2, Q3, and Q4 which do not overlap.

These four clocks make up one instruction cycle (also called machine cycle) during which one instruction is executed.

Execution of instruction starts by calling an instruction that is next in string. Instruction is called from program memory on every Q1 and is written in instruction register on Q4.

Decoding and execution of instruction are done between the next Q1 and Q4 cycles. On the following diagram we can see the relationship between instruction cycle and clock of the oscillator (OSC1) as well as that of internal clocks Q1-Q4. Program counter (PC) holds information about the address of the next instruction.

# Continued

Clock/insruction Cycle

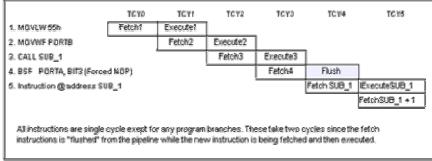

# Pipelining

Instruction Pipeline Flow

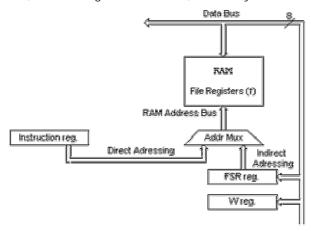

CPU

Central processing unit (CPU) is the brain of a microcontroller. That part is responsible for finding and fetching the right instruction which needs to be executed, for decoding that instruction, and finally for its execution.

Outline of the central processing unit-CPU

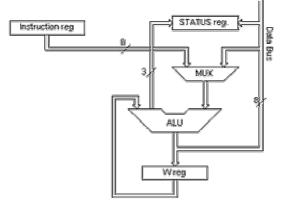

# ALU

Arithmetic logic unit is responsible for performing operations of adding, subtracting, moving (left or right within a register) and logic operations. PIC16F84 contains an 8-bit arithmetic logic unit and 8-bit work registers.

Arithmetic-logic unit and how it works

More detailed block outline of PIC16F84 microcontroller

# W Register

The W (Working Register) is the most important register. It is in the W register where all the calculations and logical manipulations such as addition, subtraction, and, or are done.

In order to move data from A to B, the data has to be move from location A to W and then from W to location B.

| ✓MOVLW | MOVe the Literal (a number) into the Working Register |

|--------|-------------------------------------------------------|

| MOVLW  | B'00100100'                                           |

| ✓MOVWF | MOVe the Working register to the file.                |

| MOVWF  | PORTB                                                 |

|        |                                                       |

| _ | Legendr |      |       |       |       |       |       |       | 1 |

|---|---------|------|-------|-------|-------|-------|-------|-------|---|

|   | 647     |      |       |       |       |       |       |       |   |

|   | IRP     | RP1  | RPO   | TO    | PD    | Z     | DC    | C     |   |

|   | RANO    | RAM6 | -3W-0 | RAV-1 | RAV-1 | R/W-> | R/W-x | R/W-x |   |

U = Unimplemented bit, read as '02 - n = Value at power-on reset

#### **STATUS Register**

bit 0 C (Carry) Transfer

Bit that is affected by operations of addition, subtraction and shifting. 1= transfer occured from the highest resulting bit 0=transfer did not occur C bit is affected by ADDWF, ADDLW, SUBLW, SUBWF instructions.

#### bit 1 DC (Digit Carry) DC Transfer

Bit affected by operations of addition, subtraction and shifting. Unlike C bit, this bit represents transfer from the fourth resulting place. It is set by addition when occurs carry from bit3 to bit4, or by subtraction when occurs borrow from bit4 to bit3, or by shifting in both direction.

R = Readable bit W = Véčable bit

1=transfer occured on the fourth bit according to the order of the result 0=transfer did not occur DC bit is affected by ADDWF, ADDLW, SUBLW, SUBWF instructions.

#### bit 2 Z (Zero bit) Indication of a zero result

This bit is set when the result of an executed arithmetic or logic operation is zero. 1=result equals zero; 0=result does not equal zero

#### *bit 3* **PD** (Power-down bit)

Bit which is set whenever power supply is brought to a microcontroller as it starts running, after each regular reset and after execution of instruction CLRWDT. Instruction SLEEP resets it when microcontroller falls into low consumption/usage regime. Its repeated setting is possible via reset or by turning the supply on, or off. Setting can be triggered also by a signal on RBO/INT pin, change on RB port, completion of writing in internal DATA EEPROM, and by a watchdog, too.

1=after supply has been turned on 0= executing SLEEP instruction

#### **STATUS Register**

bit 4 TO Time-out ; Watchdog overflow.

Bit is set after turning on the supply and execution of CLRWDT and SLEEP instructions. Bit is reset when watchdog gets to the end signaling that something is not right. 1= overflow did not occur 0= overflow did occur

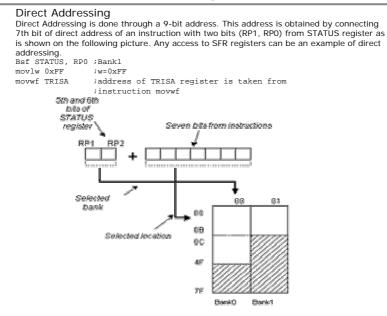

#### bit6:5 RP1:RP0 (Register Bank Select bits)

These two bits are upper part of the address for direct addressing. Since instructions which address the memory directly have only seven bits, they need one more bit in order to address all 256 bytes which is how many bytes PIC16F84 has. RP1 bit is not used, but is left for some future expansions of this microcontroller. 01=first bank 00=zero bank

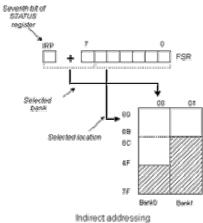

*bit 7* **IRP** (Register Bank Select bit) Bit whose role is to be an eighth bit for indirect addressing of internal RAM.

1=bank 2 and 3 0=bank 0 and 1 (from 00h to FFh)

STATUS register contains arithmetic status ALU (C, DC, Z), RESET status (TO, PD) and bits for selecting of memory bank (IRP, RP1, RP0). Considering that selection of memory bank is controlled through this register, it has to be present in each bank. STATUS register can be a destination for any instruction, with any other register. If STATUS register is a destination for instructions which affect Z, DC or C bits, then writing to these three bits is not possible.

|                                                   | Bits  | TMR0  | WDT   |  |

|---------------------------------------------------|-------|-------|-------|--|

|                                                   | 890   | 1:2   | 1:1   |  |

|                                                   | 662   | 1:4   | 1:2   |  |

|                                                   | 010   | 1:8   | 1:4   |  |

|                                                   | 62.2  | 1:18  | 1.0   |  |

|                                                   | 290   | 1:32  | 1:10  |  |

| OPTION register                                   | 2.0.2 | 1:64  | 1:32  |  |

|                                                   | 210   | 1:128 | 1:64  |  |

| bit 0:2 PSO, PS1, PS2 (Prescaler Rate Select bit) | 2.2.2 | 1:258 | 1:428 |  |

These three bits define prescaler rate select bit. What a prescaler is and how these bits can affect the work of a microcontroller will be explained in section on TMR0.

#### bit 3 PSA (Prescaler Assignment bit)

Bit which assigns prescaler between TMRO and watchdog. 1=prescaler is assigned to *watchdog* 0=prescaler is *assigned to a free-run timer TMRO*

#### bit 4 TOSE (TMR0 Source Edge Select bit)

If it is allowed to trigger TMRO by impulses from the pin RA4/TOCKI, this bit determines whether this will be to the falling or rising edge of a signal. 1=falling edge 0=rising edge

#### bit 5 TOCS (TMR0 Clock Source Select bit)

This pin enables free-run timer to increment its state either from internal oscillator on every ¼ of oscillator clock, or through external impulses on RA4/TOCKI pin. 1=external impulses 0=1/4 internal clock

#### bit 6 INTEDG (Interrupt Edge Select bit)

If interrupt is enabled possible this bit will determine the edge at which an interrupt will be activated on pin RB0/INT. 1=rising edge 0=falling edge

#### *bit 7* **RBPU** (PORTB Pull-up Enable bit)

This bit turns on and off internal 'pull-up' resistors on port B.

1 = "pull-up" resistors turned off 0 = "pull-up" resistors turned on

Relationship between TRISA and PORTA register

All port pins can be defined as input or output, according to the needs of a device that's being developed. In order to define a pin as input or output pin, the right combination of zeros and ones must be written in TRIS register. If at the appropriate place in TRIS register a logical "1" is written, then that pin is an input pin, and if the opposite is true, it's an output pin. Every port has its proper TRIS register. Thus, port A has TRISA at address 85h, and port B has TRISB at address 86h.

### Port B

PORTB has 8 pins joined to it. The appropriate register for direction of data is TRISB at address 86h.

Four pins PORTB, RB7:RB4 can cause an interrupt which occurs when their status changes from logical one into logical zero and opposite. Only pins configured as input can cause this interrupt to occur

(if any RB7: RB4 pin is configured as an output, an interrupt won't be generated at the change of status.) This interrupt option along with internal pull-up resistors makes it easier to solve common problems we find in practice like for instance that of matrix keyboard. If rows on the keyboard are connected to these pins, each push on a key will then cause an interrupt. A microcontroller will determine which key is at hand while processing an interrupt It is not recommended to refer to port B at the same time that interrupt is being processed.

The example shows how pins 0, 1, 2, and 3 are declared for input, and pins 4, 5, 6, and 7 for output.

| clrf  | STATUS      | ;BankO                         |

|-------|-------------|--------------------------------|

| clrf  | PORTB       | ;PORTB=0                       |

| bsf   | STATUS, RPO | ;Bank1                         |

| movlw | OxOF        | Defining input and output pins |

| movwf | TRISB       | Writing to TRISB register      |

### Port A

PORTA has 5 pins joined to it. The corresponding register for data direction is TRISA at address 85h.

The fifth pin of port A has dual function. On that pin is also situated an external input for timer TMRO. One of these two options is chosen by setting or resetting the TOCS bit (TMRO Clock Source Select bit). This pin enables the timer TMRO to increase its status either from internal oscillator or via external impulses on RA4/TOCKI pin.

Example shows how pins 0, 1, 2, 3, and 4 are declared to be input, and pins 5, 6, and 7 to be output pins

| bcf   | STATUS, RPO | ;BankO                                 |

|-------|-------------|----------------------------------------|

| clrf  | PORTA       | ;PORTA=0                               |

| bsf   | STATUS, RPO | ;Bank1                                 |

| movlw | Ox1F        | ;Defining input and output pins pinova |

| movwf | TRISA       | Writing to TRISA register              |

# A programming Example

|                                             | ample illustrates a sim                                      | e of a program<br>pple program written in assembly language<br>the basic rules.                                                                       |  |  |  |  |  |  |  |

|---------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Basic<br>information<br>on the •<br>program |                                                              | ; Program for initialization of port B and setting pins to status of logic one<br>; Version 1.0 Date: 10.10.1999. MCU:PIC16F84 Written by: John Smith |  |  |  |  |  |  |  |

|                                             | ; Declaration and config<br>PROCESSOR 161<br>#include "p16f8 |                                                                                                                                                       |  |  |  |  |  |  |  |

| Directive •                                 | CONFIG _CP_<br>org 0x00<br>goto Main                         | _OFF & _WDT_OFF & _PWRTE_ON & _XT_OSC<br>; Start of program<br>; Reset vector<br>; Go to the beginning of Main                                        |  |  |  |  |  |  |  |

| Inclusion of a macro                        | org 0x04<br>goto Main<br>#include "bank.i                    |                                                                                                                                                       |  |  |  |  |  |  |  |

| Comment •<br>Label •<br>Instruction •       | Main<br>BANK1<br>movfw 0x00<br>movwf TRISB<br>BANK0          | ; Beginning of the main program<br>; Select memory bank 1<br>; Port B pins are output<br>; Select memory bank 0                                       |  |  |  |  |  |  |  |

| Operand •                                   | moviw 0xFF<br>movwf PORTB<br>Loop goto Loop                  | ; Set all ones to port B<br>; Program remains in the loop                                                                                             |  |  |  |  |  |  |  |

|                                             | end                                                          | ; Necessary marking the end of a program                                                                                                              |  |  |  |  |  |  |  |

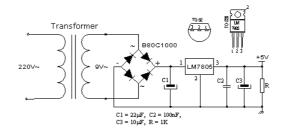

# Supplying the PIC

Generally speaking, the correct voltage supply is of utmost importance for the proper functioning of the microcontroller system. It can easily be compared to a man breathing in the air. It is more likely that a man who is breathing in fresh air will live longer than a man who's living in a polluted environment.

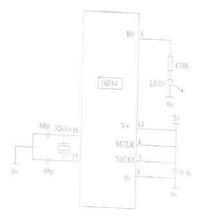

For a proper function of any microcontroller, it is necessary to provide a stable source of supply, a sure reset when you turn it on and an oscillator. According to technical specifications by the manufacturer of PIC microcontroller, supply voltage should move between 2.0V to 6.0V in all versions. The simplest solution to the source of supply is using the voltage stabilizer LM7805 which gives stable +5V on its output. One such source is shown in the picture below.

| -[]]                                                                                       | 1EST.asm                                                                                                  | 7                                                                            |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 34- <b>8</b> -1                                                                            | ×                                                                                                         |                                                                              |

| Declaring and configurin                                                                   | g a microcontroller minu                                                                                  |                                                                              |

| PROCESSOR 1684<br>Minclude "p/684 inc"                                                     |                                                                                                           |                                                                              |

| _CONFIG _CP_OF                                                                             | F&_WDT_OFF&_PWRTE_ON&_XT_OSC                                                                              |                                                                              |

| :***** Declaring variables *****                                                           |                                                                                                           | This example                                                                 |

| Coleck QxOC<br>WCYCLE<br>PRESCwait<br>endc                                                 | : Beginning of RAM<br>: Belongs to WONTX macro                                                            | initializes port B<br>as output and<br>sets logic one to<br>each pin of port |

| :***** Structure of program me                                                             | mary                                                                                                      | B to turn on all                                                             |

| ORG 0-00<br>gato Main                                                                      | ; Read vector                                                                                             | LEDs.                                                                        |

| ORG D-04<br>gata Main                                                                      | . Internapt vestor<br>: No internyt routine                                                               |                                                                              |

| Mingligde "bank ing"                                                                       | ; Assistant files                                                                                         |                                                                              |

| Main                                                                                       | : Beginning of the program                                                                                |                                                                              |

| BANKI<br>masher Gxff<br>masher BASSA<br>masher G400<br>masher G400<br>masher G400<br>BANKO | :Port A Indultation<br>1925A <: 0x8 all input<br>1908T0 indultation<br>19350 <: 0x8<br>1908T0 indultation |                                                                              |

| movier ®xif<br>moviel PORTE                                                                | ;Turn on all leds                                                                                         |                                                                              |

| Loop<br>goto Loop                                                                          | , Repeat loop                                                                                             |                                                                              |

| Eng                                                                                        | ; End of program                                                                                          |                                                                              |

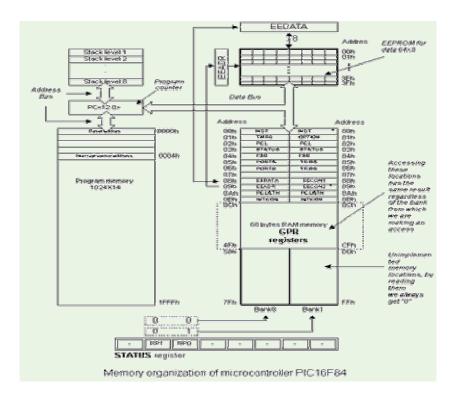

### Memory

PIC16F84 has two separate memory blocks, one for data and the other for program. EEPROM memory and GPR registers in RAM memory make up a data block, and FLASH memory makes up a program block.

#### Program memory

Program memory has been realized in FLASH technology which makes it possible to program a microcontroller many times before it's installed into a device, and even after its installment if eventual changes in program or process parameters should occur. The size of program memory is 1024 locations with 14 bits width where locations zero and four are reserved for reset and interrupt vector.

#### Data memory

Data memory consists of EEPROM and RAM memories. EEPROM memory consists of 64 eight bit locations whose contents is not lost during loosing of power supply. EEPROM is not directly addressible, but is accessed indirectly through EEADR and EEDATA registers. As EEPROM memory usually serves for storing important parameters (for example, of a given temperature in temperature regulators), there is a strict procedure for writing in EEPROM which must be followed in order to avoid accidental writing. RAM memory for data occupies space on a memory map from location 0x0C to 0x4F which comes to 68 locations. Locations of RAM memory are also called GPR registers which is an abbreviation for General Purpose Registers. GPR registers can be accessed regardless of which bank is selected at the moment.

#### SFR registers

Registers which take up first 12 locations in banks 0 and 1 are registers of specialized function assigned with certain blocks of the microcontroller. These are called Special Function Registers.

# Memory Banks

Beside this 'length' division to SFR and GPR registers, memory map is also divided in 'width' to two areas called 'banks'. Selecting one of the banks is done via RPO and RP1 bits in STATUS register

#### Example: bcf STATUS, RPO

Instruction BCF clears bit RP0 (RP0=0) in STATUS register and thus sets up bank 0.

bsf STATUS, RPO

Instruction BSF sets the bit RPO (RPO=1) in STATUS register and thus sets up bank1.

Usually, groups of instructions that are often in use, are connected into one unit which can easily be recalled in a program, and whose name has a clear meaning, so called Macros. With their use, selection between two banks becomes more clear and the program itself more legible. -20

| BANKU | macro<br>Bcf STATUS,<br>Endm | RP0 | ;Select | memory | bank | 0 | L | Locations OCh - 4Fh are general<br>purpose registers (GPR) which are<br>used as RAM memory. When location<br>8Ch - CFh in Bank 1 are accessed. w                                            |

|-------|------------------------------|-----|---------|--------|------|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BANK1 | macro<br>Bsf STATUS,<br>Endm | RPO | ;Select | memory | bank | 1 |   | actually access the exact same<br>locations in Bank 0. In other words,<br>whenever you wish to access one of<br>the GPR registers, there is no need to<br>worry about which bank we are in! |

#### **Program Counter**

Program counter (PC) is a 13 bit register that contains the address of the instruction being executed. By its incrementing or change (ex. in case of jumps) microcontroller executes program instructions step-bystep.

#### Stack

PIC16F84 has a 13-bit stack with 8 levels, or in other words, a group of 8 memory locations of 13 -bits width with special function. Its basic role is to keep the value of program counter after a jump from the main program to an address of a subprogram . In order for a program to know how to go back to the point where it started from, it has to return the value of a program counter from a stack. When moving from a program to a subprogram, program counter is being pushed onto a stack (example of this is CALL instruction). When executing instructions such as RETURN, RETLW or RETFIE which were executed at the end of a subprogram, program counter was taken from a stack so that program could continue where was stopped before it was interrupted. These operations of placing on and taking off from a program counter stack are called PUSH and POP, and are named according similar instructions on some bigger microcontrollers.

# System Programming

In order to program a program memory, microcontroller must be set to special working mode by bringing up MCLR pin to 13.5V, and supply voltage Vdd has to be stabilized between 4.5V to 5.5V.

Program memory can be programmed serially using two 'data/clock' pins which must previously be separated from device lines, so that errors wouldn't come up during programming.

# **Addressing Modes**

# Addressing Modes

#### Direct Addressing

Indirect unlike direct addressing does not take an address from an instruction but makes it with the help of IRP bit of STATUS and FSR registers. Addressed location is accessed via INDF register which in fact holds the address indicated by a FSR. In other words, any instruction which uses INDF as its register in reality accesses data indicated by a FSR register.

Let's say, for instance, that one general purpose register (GPR) at address 0Fh contains a value of 20. By writing a value of OFh in FSR register we will get a register indicator at address OFh, and by reading from INDF register, we will get a value of 20, which means that we have read from the first register its value without accessing it directly (but via FSR and INDF). It appears that this type of addressing does not have any advantages over direct addressing, but certain needs do exist during programming which can be solved smoothly only through indirect addressing.

# Addressing Modes

Reading data from INDF register when the contents of FSR register is equal to zero returns the value of zero, and writing to it results in NOP operation (no operation).

The following is an example of erasing a part of RAM memory (16 locations)

|        | Movlw OxOC  | ; initialization of starting address |

|--------|-------------|--------------------------------------|

|        | Movwf FSR   | ;FSR indicates address 0x0C          |

| LOOP   | clrf INDF   | ;INDF = O                            |

|        | incf FSR    | ;address = initial address + 1       |

|        | btfss FSR,4 | ;are all locations erased            |

|        | goto loop   | ;no, go through a loop again         |

| CONTIN | NUE         |                                      |

|        | :           | ; yes, continue with program         |

# **EEPROM** Data Memory

PIC16F84 has 64 bytes of EEPROM memory locations on addresses from 00h to 63h those can be written to or read from. The most important characteristic of this memory is that it does not loose its contents during power supply turned off. Data can be retained in EEPROM without power supply for up to 40 years (as manufacturer of PIC16F84 microcontroller states), and up to 10000 cycles of writing can be executed.

In practice, EEPROM memory is used for storing important data or some process parameters

One such parameter is a given temperature, assigned when setting up a temperature regulator to some process. If that data wasn't retained, it would be necessary to adjust a given temperature after each loss of supply. Since this is very impractical (and even dangerous), manufacturers of microcontrollers have began installing one smaller type of EEPROM memory.

EEPROM memory is placed in a special memory space and can be accessed through special registers. These registers are:

• EEDATA at address 08h, which holds read data or that to be written.

- EEADR at address 09h, which contains an address of EEPROM location being accessed.

EECON1 at address 88h, which contains control bits.

EECON2 at address 89h. This register does not exist physically and serves to protect EEPROM from accidental writing.

EECON1 register at address 88h is a control register with five implemented bits. Bits 5, 6 and 7 are not used, and by reading always are zero.

|                                   | U-0                                                        | U-0 | U-0 | R/W-1    | RAV-1 | R/W-x | R/S-0 | R/S-x |  |  |

|-----------------------------------|------------------------------------------------------------|-----|-----|----------|-------|-------|-------|-------|--|--|

|                                   | —                                                          | _   | _   | EEIF (1) | WRERR | WREN  | WR    | RD    |  |  |

|                                   | bit 7                                                      |     |     |          |       |       |       | bit 0 |  |  |

| EECON1 Register                   | Legend:                                                    |     |     |          |       |       |       |       |  |  |

| R = Readable bit W = Writable bit |                                                            |     |     |          |       |       |       |       |  |  |

|                                   | U = Unimplemented bit, read as '0' -n = Value at POR reset |     |     |          |       |       |       |       |  |  |

bit 0 RD (Read Control bit)

Setting this bit initializes transfer of data from address defined in EEADR to EEDATA register. Since time is not as essential in reading data as in writing, data from EEDATA can already be used further in the next instruction. 1=initializes reading 0=does not initialize reading

bit 1 WR (Write Control bit) Setting of this bit initializes writing data from EEDATA register to the address specified trough EEADR register. 1=initializes writing 0=does not initialize writing

bit 2 WREN (EEPROM Write Enable bit) Enables writing to EEPROM If this bit was not set, microcontroller would not allow writing to EEPROM. 1=writing allowed 0=writing disallowed

bit 3 WRERR (Write EEPROM Error Flag ) Error during writing to EEPROM This bit was set only in cases when writing to EEPROM had been interrupted by a reset signal or by running out of time in watchdog timer (if it's activated). 1=error occurred 0=error did not occur

bit 4 EEIF (EEPROM Write Operation Interrupt Flag bit) Bit used to inform that writing data to EEPROM has ended. When writing has terminated, this bit would be set automatically. Programmer must clear

EEIF bit in his program in order to detect new termination of writing 1=writing terminated 0=writing not terminated yet, or has not started

# **Reading From EEPROM**

Setting the RD bit initializes transfer of data from address found in EEADR register to EEDATA register. As in reading data we don't need so much time as in writing, data taken over from EEDATA register can already be used further in the next instruction.

| bcf   | STATUS, | RPO | ;bankO, because EEADR is at O9h |

|-------|---------|-----|---------------------------------|

| movlw | 0x00    |     | ;address of location being read |

| movwf | EEADR   |     | ;address transferred to EEADR   |

| bsf   | STATUS, | RPO | ;bank1 because EECON1 is at 88h |

| bsf   | EECON1, | RD  | reading from EEPROM;            |

| bcf   | STATUS, | RPO | ;BankO because EEDATA is at O8h |

| movf  | EEDATA, | ឃ   | ;W < EEDATA                     |

<u>After the last program instruction</u>, contents from an **EEPROM** address zero can be found in working register w.

### **Instruction Set**

#### Data transfer

Transfer of data in a microcontroller is done between **work (W) register** and an 'f' **register that represents any location in internal RAM** (regardless whether those are special or general purpose registers).

Some instructions provide for a constant being written in W register (**MOVLW** is short for MOVe Literal to W), and for data to be copied from W register onto RAM and data from RAM to be copied onto W register (or on the same RAM location, at which point only the status of Z flag changes).

Instruction **CLRF** writes constant 0 in 'f ' register, and **CLRW** writes constant 0 in register W.

SWAPF instruction exchanges places of the 4-bit nibbles field inside a register. Arithmetic and logic

Of all arithmetic operations, PIC like most microcontrollers supports only **subtraction** and **addition**. **Flags C, DC and Z** are set depending on a result of addition or subtraction. Subtraction is performed like addition of a negative value, C flag is inverse following a subtraction. In other words, it is **set if operation result is positive**, and **reset if larger number was subtracted from a smaller one**.

Logic unit of PIC has capability of performing operations **AND**, **OR**, **EX-OR**, complementing (COMF) and rotation (RLF and RRF).

Instructions which rotate the register contents move bits inside a register through flag C by one space to the left (toward bit 7), or to the right (toward bit 0). Bit which "comes out" of a register is written in flag C, and value of C flag is written in a bit on the "opposite side" of the register.

# Instruction Set

#### **Bit operations**

Instructions BCF and BSF do setting or cleaning of one bit anywhere in the memory. Even though this seems like a simple operation, it is executed so that CPU first reads the whole byte, changes one bit in it and then writes in the entire byte at the same place.

#### **Instruction Execution Period**

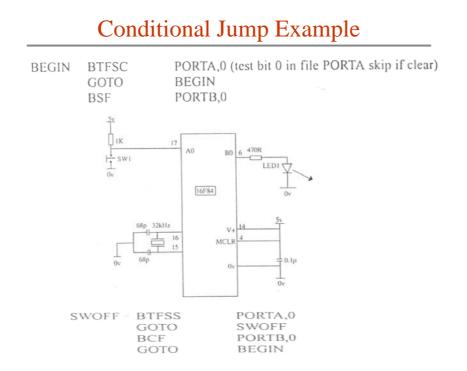

All instructions are executed in one cycle except for conditional branch instructions if condition was true, or if the contents of program counter was changed by some instruction.

In that case, execution requires two instruction cycles, and the second cycle is executed as NOP (No Operation). Four oscillator clocks make up one instruction cycle.

If we are using an oscillator with 4MHz frequency, the normal time for executing an instruction is 1  $\mu$ s, and in case of conditional branching, execution period is 2  $\mu$ s.

# **Instruction Set**

#### PIC16F84 INSTRUCTION SET

#### Literal and control instructions:

| Mnemor  | nic | Description                                | Function                                        |

|---------|-----|--------------------------------------------|-------------------------------------------------|

| addiw 🛛 | k   | Add literal to W                           | $k + W \rightarrow W$                           |

| andlw   | k   | AND literal and W                          | $k$ .AND. $W \rightarrow W$                     |

| call    | k   | Call subroutine                            | $PC + 1 \rightarrow TOS, k \rightarrow PC$      |

| cirwdt  |     | Clear watchdog timer                       | $0 \rightarrow$ WDT (and prescaler if assigned) |

| goto    | k   | Goto address (k is nine bits)              | $k \rightarrow PC$ (9 bits)                     |

| iorlw   | k   | Incl. OR literal and W                     | $k : OR: W \rightarrow W$                       |

| movlw   | k   | Move Literal to W                          | $k \rightarrow W$                               |

| option  |     | Load OPTION register                       | $W \rightarrow OPTION Register$                 |

| retfie  |     | Return from Interrupt                      | TOS $\rightarrow$ PC, 1 $\rightarrow$ GIE       |

| retlw   | k   | Return with literal in W                   | $k \rightarrow W$ , TOS $\rightarrow$ PC        |

| return  |     | Return from subroutine                     | $TOS \rightarrow PC$                            |

| sleep   |     | Go into Standby Mode                       | $0 \rightarrow WDT$ , stop oscillator           |

| sublw   | k   | Subtract W from literal                    | $K \cdot W \to W$                               |

| tris    | f   | Configure port f (downward compat. instr.) | W $\rightarrow$ I/O control reg f               |

| xorlw   | k   | Exclusive OR literal and W                 | k .XOR. W $\rightarrow$ W                       |

| Field |                                           | Des                                         | cription                         |  |  |

|-------|-------------------------------------------|---------------------------------------------|----------------------------------|--|--|

| R ⊨   | Bit address within an 8-bit file register |                                             |                                  |  |  |

| d     | Destination select;                       | Destination select; d = 0 Store result in W |                                  |  |  |

|       |                                           | d = 1                                       | Store result in file register f. |  |  |

|       |                                           |                                             | Default is d = 1.                |  |  |

| f     | Register file address (0x00 to 0xFF)      |                                             |                                  |  |  |

| k     | Literal field, constant data or label     |                                             |                                  |  |  |

| W     | Working register (accumi                  | Working register (accumulator)              |                                  |  |  |

Instruction Set

| Field | Description                               |         |                              |  |  |

|-------|-------------------------------------------|---------|------------------------------|--|--|

| R + + | Dit address within an 8-bit file register |         |                              |  |  |

| 4     | Destination select.                       | 4+0     | Store result in W            |  |  |

|       |                                           | d+1     | Otom repullin the register C |  |  |

|       |                                           |         | Default is div 1.            |  |  |

| 1     | Register Tel address (D40 ts 047)         |         |                              |  |  |

| *     | Ubmail field, constant data or label      |         |                              |  |  |

| 15    | Working register (accume                  | viator) |                              |  |  |

| addwff,dAdd W and f $W + f \rightarrow d$ andwff,dAND W and fWAND. $f \rightarrow d$ clrffClear f $0 \rightarrow f$ clrwClear W $0 \rightarrow W$ comff,dComplement fNOT. $f \rightarrow d$ decff,dDecrement f $f - \rightarrow d$ decfszf,dDecrement f $f - 1 \rightarrow d$ , skip if 0incfszf,dIncrement f $f + 1 \rightarrow d$ incfszf,dIncrement f $f + 1 \rightarrow d$ iorwff,dInclusive OR W and f $W \cdot OR, f \rightarrow d$ mowffMove f $f \rightarrow d$ mowffMove f $f \rightarrow d$ register fregister f $7$ reff,dRotate left f $\downarrow$ c $\rightarrow$ register f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | AND W and f<br>Clear f<br>Clear W<br>Complement f<br>Decrement f<br>Decrement f, skip if zero<br>Increment f | $ \begin{array}{c} W  \text{AND.} \ f \rightarrow d \\ 0 \rightarrow f \\ 0 \rightarrow W \\ \text{.NOT.} \ f \rightarrow d \\ f  - \rightarrow d \\ f  1 \rightarrow d, \ \text{skip if } 0 \end{array} $ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clear f<br>Clear W<br>Complement f<br>Decrement f<br>Decrement f, skip if zero<br>Increment f                | $\begin{array}{c} 0 \rightarrow f \\ 0 \rightarrow W \\ .NOT. \ f \rightarrow d \\ f \ - \ \rightarrow d \\ f \ - \ 1 \rightarrow d, \ skip \ if 0 \end{array}$                                            |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Clear W<br>Complement f<br>Decrement f<br>Decrement f, skip if zero<br>Increment f                           | $\begin{array}{c} 0 \rightarrow W \\ .NOT. \ f \rightarrow d \\ f \ - \ \rightarrow d, \ skip \ if 0 \end{array}$                                                                                          |

| $\begin{array}{cccc} \operatorname{comf} & \mathrm{f}, \mathrm{d} & \operatorname{Complementf} & .\operatorname{NOT.} \mathbf{f} \to \mathrm{d} \\ \mathrm{decf} & \mathrm{f}, \mathrm{d} & \operatorname{Decrementf} & \mathrm{f} - \to \mathrm{d} \\ \mathrm{decfsz} & \mathrm{f}, \mathrm{d} & \operatorname{Decrementf} & \mathrm{f} + 1 \to \mathrm{d} \\ \mathrm{incrementf} & \mathrm{incrementf} & \mathrm{f} + 1 \to \mathrm{d} \\ \mathrm{incrementf} & \mathrm{incrementf} & \mathrm{f} + 1 \to \mathrm{d} \\ \mathrm{incrementf} & \mathrm{incrementf} & \mathrm{incrementf} \\ \mathrm{incrementf} \\ \mathrm{incrementf} & \mathrm{incrementf} \\ \mathrm{incrementf} \\$ | Complement f<br>Decrement f<br>Decrement f, skip if zero<br>Increment f                                      | .NOT. $f \rightarrow d$<br>$f - \rightarrow d$<br>$f - 1 \rightarrow d$ , skip if 0                                                                                                                        |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decrement f<br>Decrement f, skip if zero<br>Increment f                                                      | $f \cdot \rightarrow d$<br>$f \cdot 1 \rightarrow d$ , skip if 0                                                                                                                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Decrement f, skip if zero<br>Increment f                                                                     | f - 1 $\rightarrow$ d, skip if 0                                                                                                                                                                           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Increment f                                                                                                  |                                                                                                                                                                                                            |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              | $f + 1 \rightarrow d$                                                                                                                                                                                      |

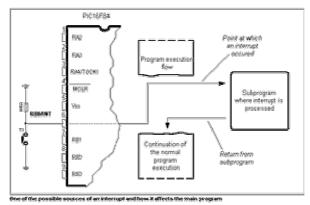

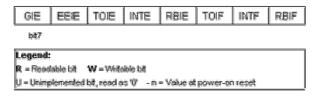

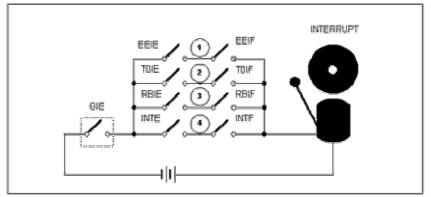

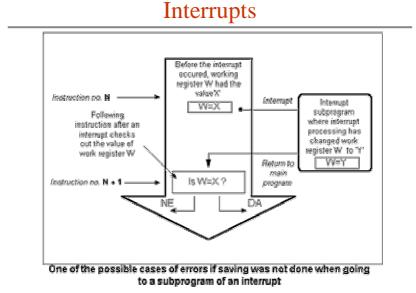

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Increment f. skin if zero                                                                                    |                                                                                                                                                                                                            |